Un “délire” commencé en 2015.

Je trouvais le gros câble du multipaire analogique trop lourd et “difficile” à manipuler.

Et en tant qu’amateur, difficile de m’offrir une solution numérique à partir du boitier de scène.

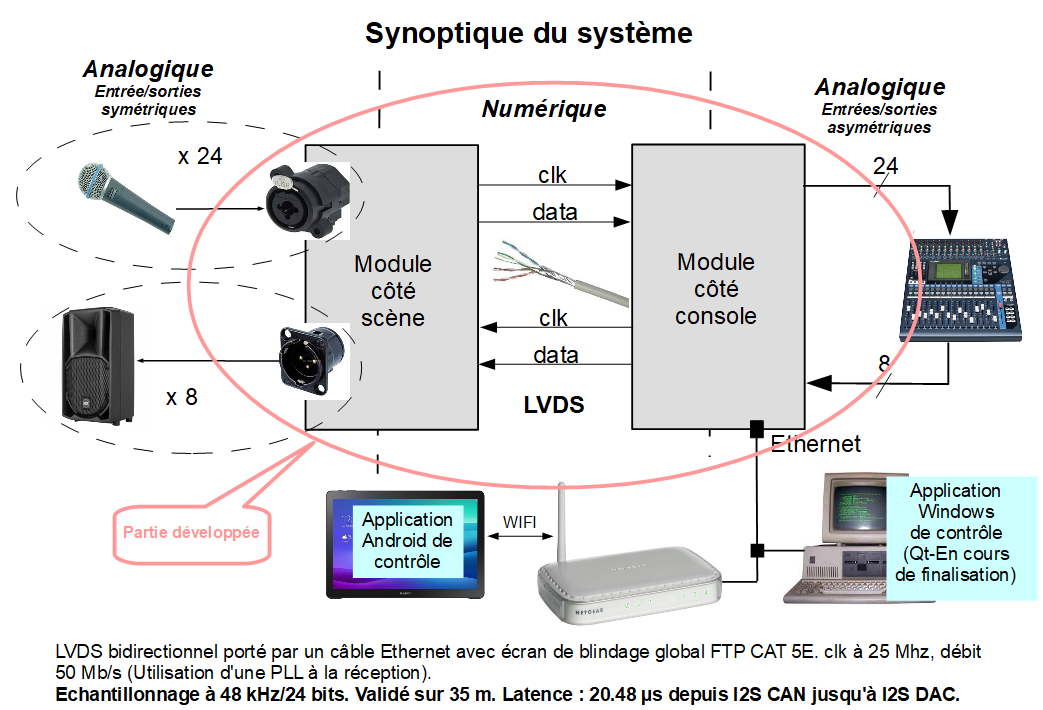

Les caractéristiques principales sont:

- Transmission numérique sur 24 bits / 48 Khz

- Latence : 20.48 µs depuis I2S CAN d’un module jusqu’à I2S DAC de l’autre module

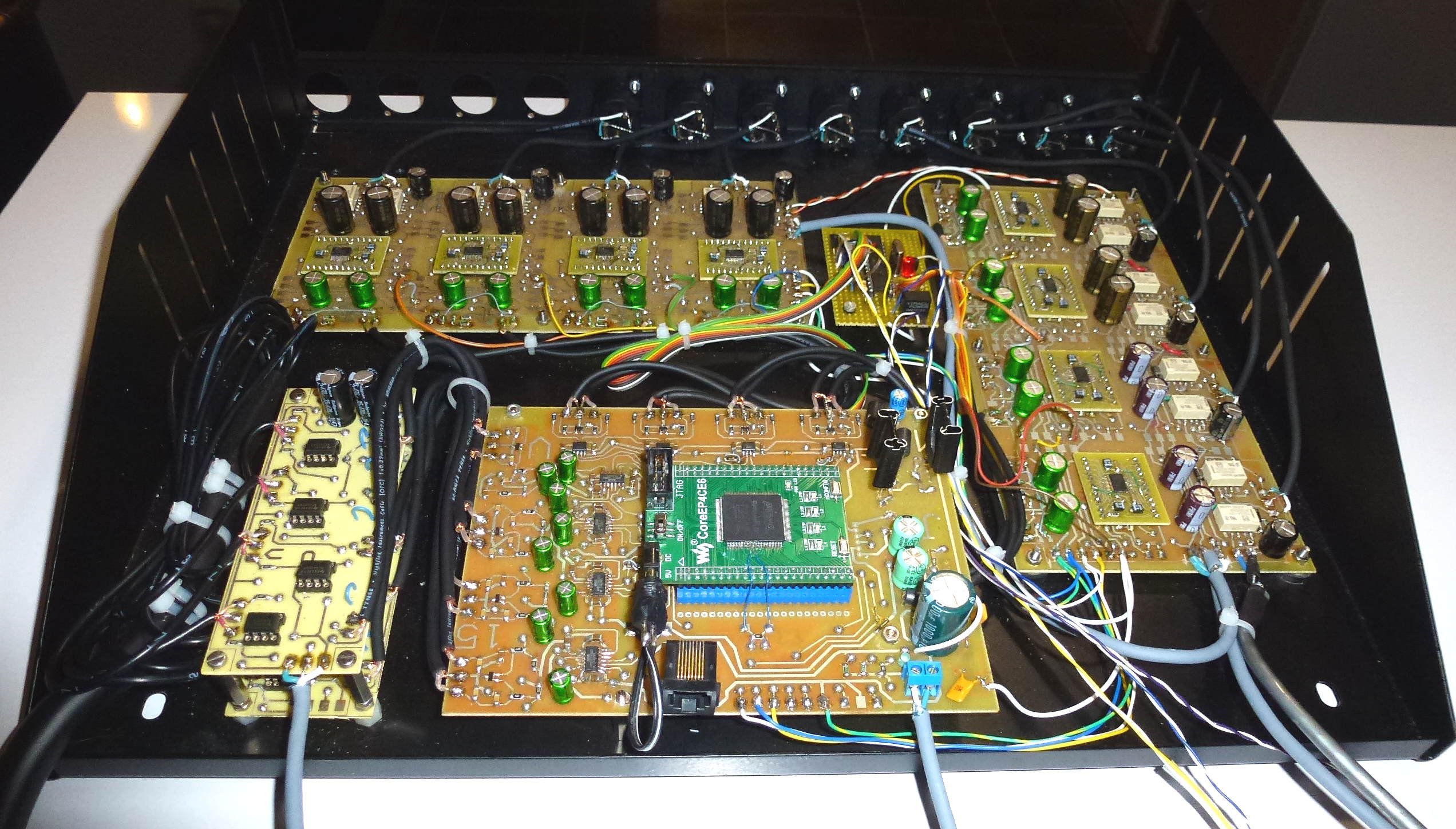

- 24 Préamplis micro haute qualité (PGA2505) sur le module de scène. Le gain est à commande numérique et peut donc être réglé à distance.

- Validé sur 35 m

- PAD (-20 dB) et 48 V Phantom commutables à distance sur chaque voie micro

- Paramétrage à distance des préamplis depuis une application de contrôle Android (Gain, PAD, 48 V Phantom). Application PC (Sous QT) en cours de finalisation.

- Visualisation sur l’application de la “présence signal” et du clip de chaque voie

- LED sur chaque module indiquant qu’une voie au moins clippe. Une consultation sur l’application de contrôle permet de définir la(les)quelle(s) afin de modifier le gain

- Mémorisation de la configuration (Gain, PAD, 48 V de chaque voie) en mémoire F-RAM. Ainsi, le système retrouve la configuration précédente à chaque mise sous tension.

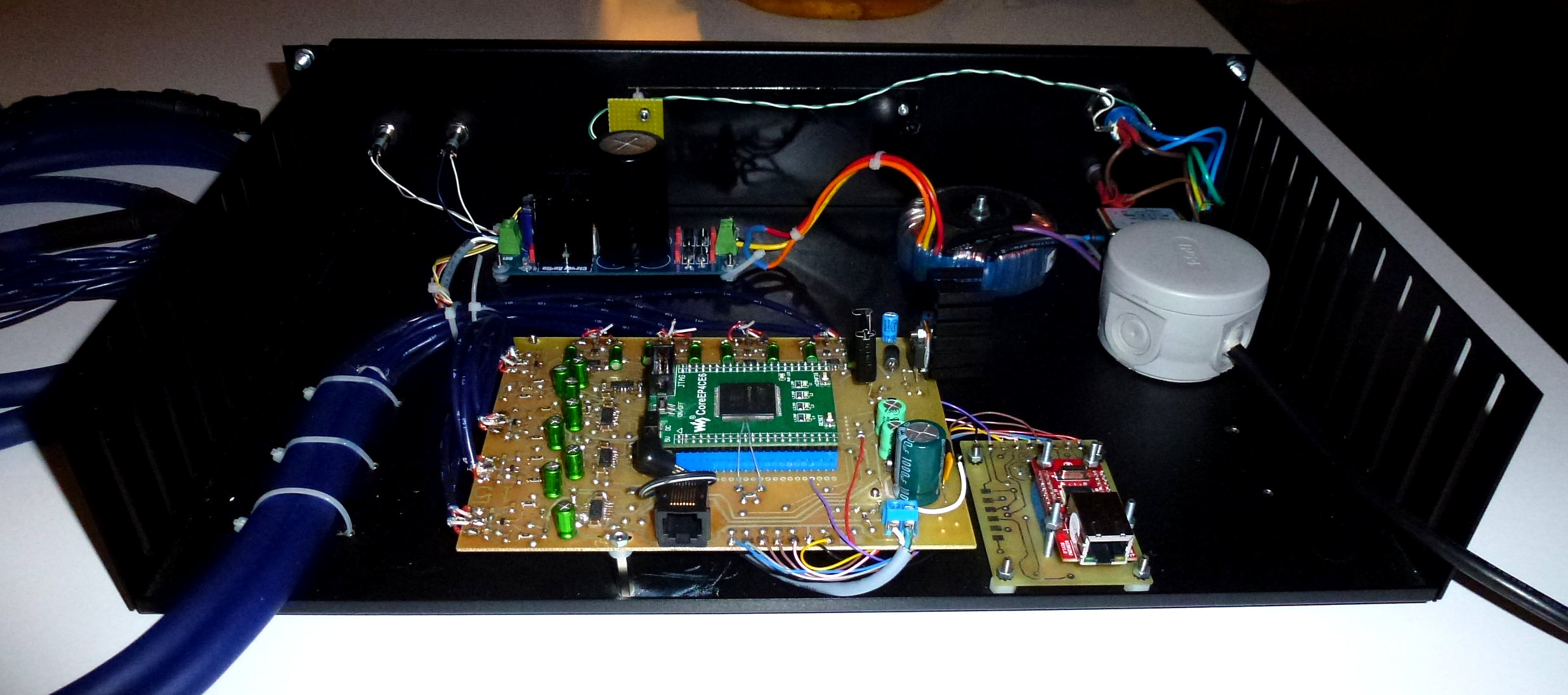

Faute de temps, Il n’y a que 8 voies réalisées dans le sens scène vers console pour le moment. Toutefois, le traitement numérique fonctionne déjà pour 24 voies.

Tout est donné sur les liens ci-dessous:

Designs VHDL, Sources C des microcontôleurs softcores embarqués dans les FPGA et du microcrontrôleur PIC de multiplexage des “clips”, description des trames LVDS et d’échanges avec l’application de contrôle, Java de l’application de contrôle sous Android. J’ai essayé de commenter un maximum, sauf l’application Android, que j’ai laissée “dans son jus”, développée sous Android Studio.

Je ne donne aucun typon. De toutes façons, il y a eu trop de corrections. A votre EDA préféré !

A noter : Cette présentation n’est pas un “tuto”. Comprendre ce qui est exposé impose des prérequis. Si tout cela peut servir à un projet d’études, l’objectif sera alors atteint.

Les développements ont été effectués sous Quartus II 14.0 / Nios II 14.0 Software Build Tools for Eclipse / Modelsim 10.1e. On considère que ces environnements sont un minimum maitrisés.

A savoir!:

– Un élément mineur a volontairement été retiré dans le design VHDL. Néanmoins, cela empêche – sans danger – le fonctionnement du système;

– Une résistance manque sur un schéma. Son absence est aussi sans danger mais sa présence est indispensable.

Il suffit de me contacter gentiment pour obtenir (gratuitement!) les corrections. L’objectif de la manœuvre est d’essayer pour moi de recenser les personnes intéressées par le projet.

- Commun aux deux parties

- Propre à la partie côté scène

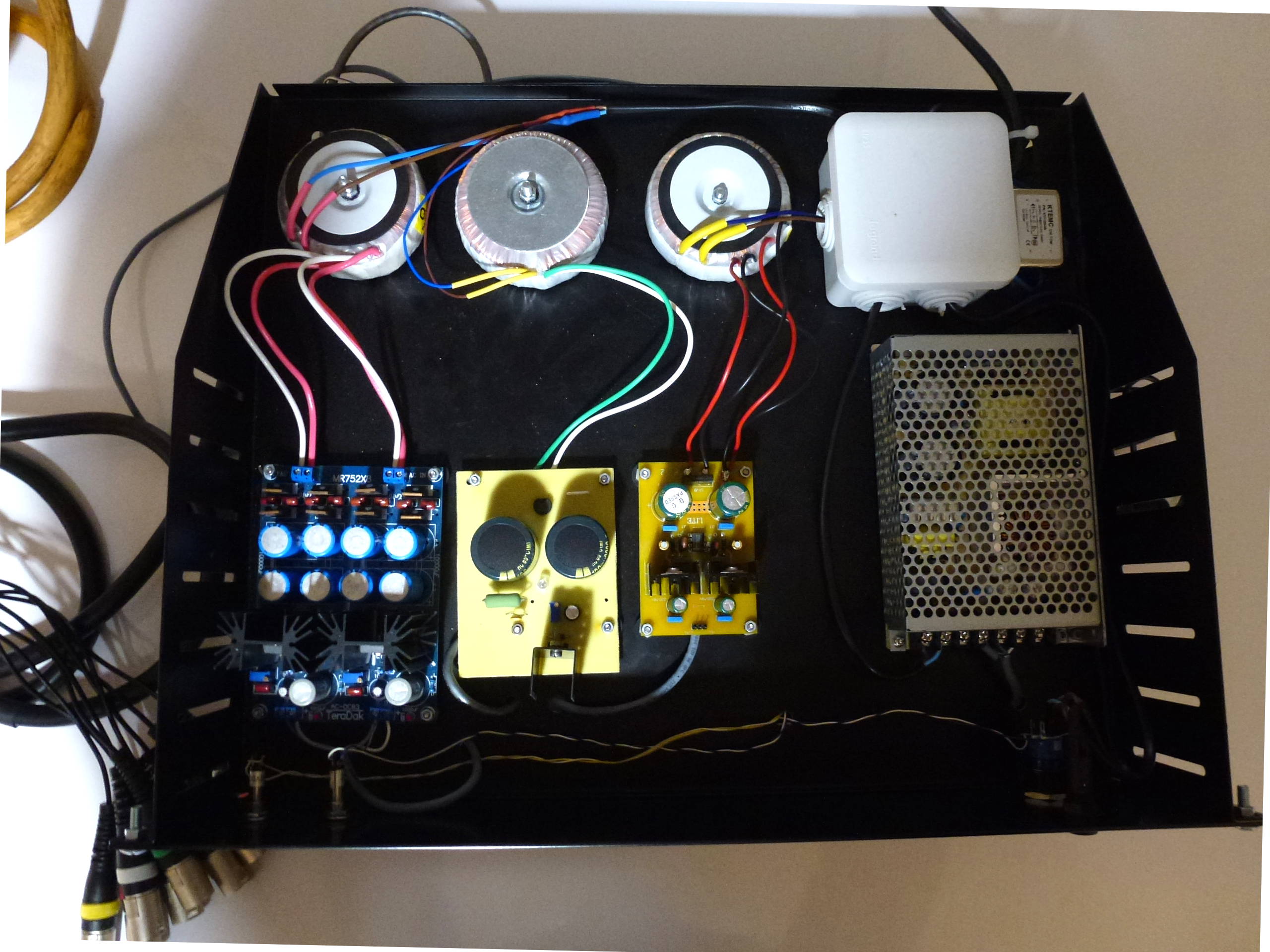

- Propre à la partie côté console

- Application de contrôle

- Simulation du design VHDL

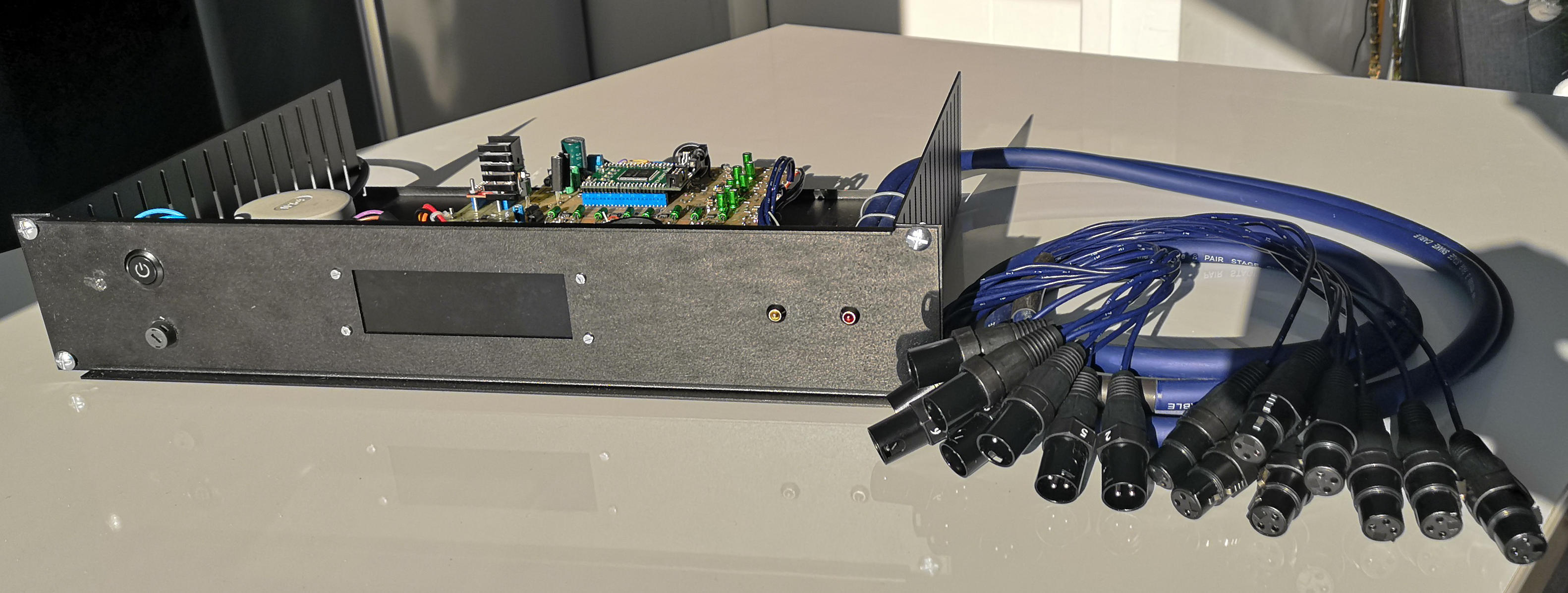

8 XLR mâles pour récupérer les 8 premières voies (micros, …) entrées sur le module de scène.

8 XLR femelles pour l’envoi des sorties de la console vers les amplis de la façade et des retours.